#### Second Edition (October 1990)

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time.

It is possible that this publication may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Requests for technical information about IBM products should be made to your IBM Authorized Dealer or your IBM Marketing Representative.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577.

# © Copyright International Business Machines Corporation 1989, 1990. All rights reserved.

Note to U.S. Government Users — Documentation related to restricted rights — Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

## **Special Notices**

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product, program or service is not intended to state or imply that only IBM's product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any of IBM's intellectual property rights or other legally protectible rights may be used instead of the IBM product, program, or service. Evaluation and verification of operation in conjunction with other products, programs, or services, except those expressly designated by IBM, are the user's responsibility.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577.

The following terms, denoted by an asterisk (\*) in this publication, are trademarks of the IBM Corporation in the United States and/or other countries:

IBM Micro Channel Personal Computer AT Personal System/2 PS/2

The following terms, denoted by a double asterisk (\*\*) in this publication, are trademarks of other companies as follows:

Hitachi Corporation

Intel Intel Corporation

Motorola Motorola, Incorporated

## **Preface**

This technical reference contains hardware and software interface information specific to the IBM Personal System/2 Model 60 computer. It is intended for those who develop hardware and software products for these systems. Users should understand computer architecture and programming concepts.

This publication consists of the following sections:

Section 1, "System Overview," describes the system, features and specifications.

Section 2, "Programmable Option Select," describes registers used for configuration.

Section 3, "System Board," describes the system specific hardware implementations.

This technical reference should be used with the following publications:

IBM Personal System/2 Hardware Interface Technical Reference

— Architectures

IBM Personal System/2 Hardware Interface Technical Reference

— Common Interfaces

IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference

These publications contain additional information on many of the subjects discussed in this technical reference.

**Warning:** The term "Reserved" describes certain signals, bits, and registers that should not be changed. Use of reserved areas can cause compatibility problems, loss of data, or permanent damage to the hardware. When the contents of a register are changed, the state of the reserved bits must be preserved. When possible, read the register first and change only the bits that must be changed.

# Contents

| Section 1. System Overview                              | 1-1  |

|---------------------------------------------------------|------|

| Description                                             |      |

| System Board Features                                   |      |

| System Board Block Diagram                              | 1-5  |

| System Board I/O Address Map                            | 1-6  |

| Specifications                                          | 1-7  |

|                                                         | 1-10 |

|                                                         | 1-10 |

| Output Protection                                       | 1-11 |

|                                                         | 1-11 |

|                                                         | 1-11 |

| Section 2. Droggements Ontion Salest                    | 0.4  |

| Section 2. Programmable Option Select                   |      |

|                                                         |      |

| POS Address Map                                         |      |

| Card Selected Feedback                                  |      |

| System Board Setup                                      |      |

| System Board Enable/Setup Register (Hex 0094)           |      |

| System Board POS Register 2 (Hex 0102)                  |      |

| System Board POS Register 3 (Hex 0103)                  | 2-9  |

| Adapter Enable/Setup Register (Hex 0096)                | 2-10 |

| Section 3. System Board                                 | 3-1  |

| Description                                             | 3-3  |

| Micro Channel Implementation                            | 3-3  |

| Exception Reporting                                     |      |

| Adapter Identification                                  | 3-3  |

| Central Arbiter                                         |      |

| Memory                                                  |      |

| Read-Only Memory Subsystem                              | 3-7  |

| Random Access Memory Subsystem                          | 3-7  |

| Real-Time Clock/Complementary Metal-Oxide Semiconductor |      |

|                                                         | 3-10 |

|                                                         | 3-20 |

| •                                                       | 3-20 |

|                                                         | 3-20 |

|                                                         | 3-21 |

|                                                         | 3-23 |

|                                                         | 3-24 |

|                                                         |      |

# **Figures**

| 1-1.         | System Board Devices and Features                |       |

|--------------|--------------------------------------------------|-------|

| 1-2.         | System Board                                     | . 1-5 |

| 1-3.         | System Board I/O Address Map                     | . 1-6 |

| 1-4.         | Performance Specifications — System Board        | . 1-7 |

| 1-5.         | Physical Specifications                          | . 1-8 |

| 1-6.         | Acoustical Readings                              |       |

| 1-7.         | Component Maximum Current                        | 1-10  |

| 1-8.         | Channel Load Current                             | 1-10  |

| 1-9.         | Voltage Assignments for the Internal Drive       |       |

|              | Power-Supply Connectors                          |       |

| 2-1.         | POS I/O Address Map                              |       |

| 2-2.         | Card Selected Feedback Register (Hex 0091)       |       |

| 2-3.         | System Board Enable/Setup Register (Hex 0094)    |       |

| 2-4.         | System Board POS Register 2 (Hex 0102)           |       |

| 2-5.         | Parallel Port Select Bits                        |       |

| <b>2-6</b> . | System Board POS Register (Hex 0103)             |       |

| 2-7.         | Adapter Enable/Setup Register (Hex 0096)         |       |

| 3-1.         | Arbitration Bus Priority Assignments             |       |

| 3-2.         | Arbitration Register, Write to Hex 0090          |       |

| 3-3.         | Arbitration Register, Read Hex 0090              |       |

| 3-4.         | System Memory Map                                | . 3-8 |

| 3-5.         | System Board Memory Connector                    |       |

| 3-6.         | RT/CMOS RAM Address Map                          | 3-10  |

| 3-7.         | RT/CMOS Address Register and NMI Mask (Hex 0070) | 3-11  |

| 3-8.         | RT/CMOS Data Register (Hex 0071)                 |       |

| 3-9.         | Real-Time Clock Bytes                            |       |

| 3-10.        | Status Register A                                |       |

| 3-11.        | Status Register B                                |       |

| 3-12.        | Status Register C                                |       |

| 3-13.        | Status Register D                                |       |

| 3-14.        | Diagnostic Status Byte                           |       |

| 3-15.        | Diskette Drive Type Byte                         |       |

| 3-16.        | Diskette Drive Type Byte (Bits 7 - 4)            | 3-17  |

| 3-17.        |                                                  |       |

| 3-18.        | Equipment Byte                                   |       |

| 3-19.        | Equipment Byte (Bits 7, 6)                       |       |

| 3-20.        | Equipment Byte (Bits 5, 4)                       |       |

| 3-21.        | System Control Port B (Write)                    |       |

| 3-22.        | System Control Port B (Read)                     |       |

| 3-23.        | System Control Port A (Hex 0092)                 | 3-21  |

# Section 1. System Overview

| Description                  | . 1-3 |

|------------------------------|-------|

| System Board Features        | . 1-3 |

| System Board Block Diagram   | . 1-5 |

| System Board I/O Address Map | . 1-6 |

| Specifications               | . 1-7 |

| Power Supply                 |       |

| Outputs                      | 1-10  |

| Output Protection            |       |

| Voltage Sequencing           |       |

| Power Supply Connectors      | 1-11  |

**Notes:**

### **Description**

The IBM' Personal System/2' Model 60 computer is a self-contained, | floor-standing system that features the Micro Channel' architecture. | It comes with a keyboard, and can support two diskette drives and | two internal fixed disk drives.

Programs can identify the system by reading the model and submodel bytes. The model and submodel byte for this system is hex FC and 05, respectively. Interrupt hex 15, function code (AH) = hex C0, returns the model and submodel bytes and BIOS revision code.

Refer to the IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference for a listing of other systems, and check the supplements section for updates to that listing.

## **System Board Features**

The following figure lists the system board devices and features. The Hardware Interface Technical Reference manuals describe all devices common to PS/2\* products by type number.

IBM, Personal System/2, PS/2, and Micro Channel are trademarks of the International Business Machines Corporation.

| Device               | Туре | Features                                               |

|----------------------|------|--------------------------------------------------------|

| Microprocessor       |      | 80286                                                  |

|                      |      | 24-bit address and 16-bit                              |

|                      |      | data interface                                         |

| System Timers        | 1    | Channel 0 - System timer                               |

|                      |      | Channel 2 - Tone generation                            |

|                      |      | for speaker                                            |

|                      |      | Channel 3 - Watchdog timer                             |

| ROM Subsystem        |      | 128KB (KB = 1024 bytes)                                |

| RAM Subsystem        |      | 1MB (MB = 1,048,576 bytes)                             |

| _                    |      | Expandable on the channel                              |

| CMOS RAM             |      | 64-byte CMOS RAM with                                  |

| Subsystem            |      | real-time clock/calendar                               |

|                      |      | 2KB CMOS RAM extension                                 |

|                      |      | Battery backup                                         |

| Video Subsystem      | 1    | Auxiliary connector on the channel                     |

|                      | •    | Analog output                                          |

|                      |      | 256KB video memory                                     |

| Audio Subsystem      | 1    |                                                        |

| Addio Sabsystein     | ,    | Driven by:                                             |

|                      |      | - System-timer channel 2                               |

| DMA Controller       |      | - The 'audio sum node' signal.                         |

| DMA CONTROller       | 1    | Eight independent DMA channels                         |

|                      |      | Single or burst transfers and                          |

|                      | _    | read verification                                      |

| interrupt Controller | 1    | 16 levels of system interrupts                         |

|                      |      | Interrupts are level-sensitive                         |

| Keyboard/Auxiliary   | 1    | Keyboard connector                                     |

| Device Controller    |      | Auxiliary device connector                             |

|                      |      | Password security                                      |

| Diskette Drive       | 1    | Supports:                                              |

| Controller           |      | <ul> <li>720KB formatted diskette density</li> </ul>   |

|                      |      | <ul> <li>1.44MB formatted diskette density.</li> </ul> |

| Serial Controller    | 1, 2 | RS-232C interface                                      |

|                      |      | Programmable as serial port 1 or 2                     |

|                      |      | FIFO mode* and character mode                          |

| Paraliel Controller  | 1    | Programmable as parallel port 1, 2, or 3               |

|                      | •    | Supports bidirectional input and output                |

| Micro Channel        |      | Eight channel connectors for                           |

|                      |      | Type 3 adapters                                        |

|                      |      | - 8- or 16-bit device support                          |

|                      |      | - One with an auxiliary video                          |

|                      |      | extension                                              |

|                      |      |                                                        |

|                      |      | - One occupied by the fixed disk                       |

| Math Coprocessor     |      | drive adapter                                          |

| Socket               |      | Supports 80287 math coprocessors                       |

| JOURGE               |      | Same clock speed as the system microprocessor          |

|                      |      |                                                        |

Figure 1-1. System Board Devices and Features

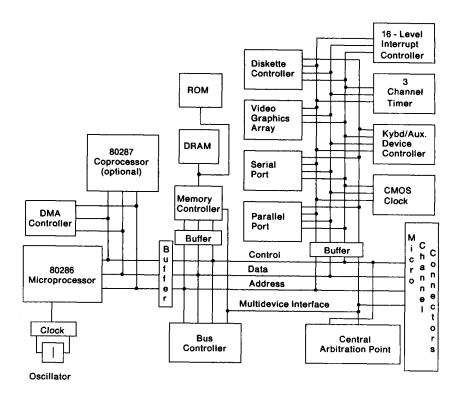

# System Board Block Diagram

Figure 1-2. System Board

# System Board I/O Address Map

| Hex Addresses           | Device                             |

|-------------------------|------------------------------------|

| 0000 - 001F             | DMA Controller (0 - 3)             |

| 0020, 0021              | Interrupt Controller (Master)      |

| 0040, 0042 - 0044, 0047 | System Timers                      |

| 0060                    | Keyboard, Auxiliary Device         |

| 0061                    | System Control Port B              |

| 0064                    | Keyboard, Auxiliary Device         |

| 0070, 0071              | RT/CMOS and NMI Mask               |

| 0081 - 0083, 0087       | DMA Page Registers (0 - 3)         |

| 0089, 008A, 008B, 008F  | DMA Page Registers (4 - 7)         |

| 0090                    | Central Arbitration Control Point  |

| 0091                    | Card Selected Feedback Register    |

| 0092                    | System Control Port A              |

| 0094                    | System Board Enable/Setup Register |

| 0096                    | Adapter Enable/Setup Register      |

| 00A0 - 00A1             | Interrupt Controller (Slave)       |

| 00C0 - 00DF             | DMA Controller (4 - 7)             |

| 00F0 - 00FF             | Math Coprocessor                   |

| 0100 - 0107             | Programmable Option Select         |

| 01F0 - 01F8             | Fixed Disk Drive Controller        |

| 0278 - 027B             | Parallel Port 3                    |

| 02F8 - 02FF             | Serial Port 2 (RS-232C)            |

| 0378 - 037B             | Parallel Port 2                    |

| 03B4, 03B5, 03BA        | Video Subsystem                    |

| 03BC - 03BF             | Parallel Port 1                    |

| 03C0 - 03C5             | Video Subsystem                    |

| 03C6 - 03C9             | Video DAC                          |

| 03CA, 03CC, 03CE, 03CF  | Video Subsystem                    |

| 03D4, 03D5, 03DA        | Video Subsystem                    |

| 03F0 - 03F7             | Diskette Drive Controller          |

| 03F8 - 03FF             | Serial Port 1 (RS-232C)            |

Figure 1-3. System Board I/O Address Map

# **Specifications**

| The following figure describes system board performance.

| Device               |                           | Number of Walts | Cycle Time (ns) |

|----------------------|---------------------------|-----------------|-----------------|

| Microprocessor (10   | MHz - 100 ns Clock):      |                 |                 |

| Access to System     | Board RAM                 | 1               | 300             |

| Access to System     | Board ROM                 | 1               | 300             |

| Access to Channe     | l:                        |                 |                 |

| Default Transfer     | Cycle:                    |                 |                 |

| I/O Access           |                           | 1               | 300             |

| Memory Access        | \$                        | 0               | 200             |

| Synchronous Ext      | ended Transfer Cycle      | 1               | 300             |

| Refresh Rate         |                           |                 | 500 (min)       |

| (Typically perform   | ed every 15.1 <i>µ</i> s) |                 |                 |

| Bus Master Access    | to System Board RAM       |                 | 300 (min)       |

| DMA Controller (10   | MHz - 100 ns Clock):      |                 |                 |

| Single Transfer:     | 300 + I/O Access + Memo   | ry Access       |                 |

| Burst Transfers:     | 300 + (I/O Access + Mem   | ory Access)N *  |                 |

| System Board Me      | mory Access               |                 | 300             |

| Default Transfer C   | Cycle:                    |                 |                 |

| I/O Access           |                           |                 | 300             |

| Memory Access        |                           |                 | 200             |

| Synchronous Exte     | nded Transfer Cycle       |                 | 300             |

| * N is the number of | f transfers in the burst. |                 |                 |

Figure 1-4. Performance Specifications — System Board

| The following figure describes physical specifications of the system.

| Size:                               |                                             |

|-------------------------------------|---------------------------------------------|

| Width                               | 165 mm (6.5 in)                             |

| Width (Feet extended)               | 318 mm (12.5 in)                            |

| Depth                               | 483 mm (19.0 in)                            |

| Height                              | 597 mm (23.5 in)                            |

| Weight                              | 20 kg (44 lb) with one fixed disk drive     |

| Cables:                             |                                             |

| Power Cable                         | 1.8 m (6 ft)                                |

| Keyboard Cable                      | 3.05 m (10 ft)                              |

| Air Temperature:                    |                                             |

| System On                           | 15.6 to 32.2°C (60 to 90°F)                 |

| System Off                          | 10.0 to 43.0°C (50 to 110°F)                |

| Humidity:                           |                                             |

| System On                           | 8% to 80%                                   |

| System Off                          | 8% to 80%                                   |

| Maximum Altitude                    | 2133.6 m (7000 ft)                          |

| Heat Output:                        |                                             |

| 207 Watt Power Supply               | 320 Watts (1100 BTUs/hour)                  |

| 225 Watt Power Supply               | 350 Watts (1200 BTUs/hour)                  |

| 250 Watt Power Supply               | 390 Watts (1330 BTUs/hour)                  |

| Acoustical Readings                 | (See Figure 1-6 on page 1-9)                |

| Electrical Input:                   |                                             |

| Input Voltage (Range is automatical | ally selected; sinewave input is required): |

| Low Hange                           | 90 (min) - 137 (max) Vac                    |

| High Range                          | 180 (min) - 265 (max)Vac                    |

| Frequency:                          |                                             |

| Low Range                           | 47 (min) - 53 (max) Hz                      |

| High Range                          | 57 (min) - 63 (max) Hz                      |

| Input in Kilovolt-Ampere (kVA):     |                                             |

| Minimum configuration               |                                             |

| (as shipped by IBM)                 | 0.10 kVA                                    |

| Maximum configuration:              |                                             |

| 207 Watt Power Supply               | 0.53 kVA                                    |

| 225 Watt Power Supply               | 0.58 kVA                                    |

| 250 Watt Power Supply               | 0.65 kVA                                    |

| Electromagnetic Compatibility       | FCC Class B                                 |

Figure 1-5. Physical Specifications

### | The following figure describes the acoustical readings of the system.

|                                | L <sub>WAd</sub> in I |           | L <sub>pAm</sub> in d           | В          | <l<sub>pA&gt;<sub>m</sub></l<sub> |         |

|--------------------------------|-----------------------|-----------|---------------------------------|------------|-----------------------------------|---------|

| Description                    | Operate               | ldle      | Operate                         | ldle       | Operate                           | ldle    |

| Model 60                       | 5.1                   | 5.1       | 41                              | 40         | 38                                | 37      |

| Notes:                         |                       |           |                                 |            |                                   |         |

| Ł <sub>WAd</sub> is the d      | leclared soun         | d power   | level for the                   | random s   | ample of mad                      | chines. |

| PAIN                           |                       |           | eighted sound<br>) for the rand | •          |                                   |         |

| νA III                         |                       |           | A-weighted so<br>the random s   | •          |                                   | it the  |

| All measureme<br>conformance w |                       |           | ce with ANSI                    | S12.10, a  | and reported                      | in      |

| The measurem                   | ents are prel         | iminary o | data and subj                   | ect to cha | ange.                             |         |

| Figure 1-6. Acoustical Readings

# **Power Supply**

The power supply requires a sinewave input and converts the ac input voltage to three dc output voltages. The power supply provides power for the following:

- System board

- Channel adapters

- · Internal diskette drives

- · Internal fixed disk drives

- Auxiliary device

- Keyboard.

The power switch and one light-emitting diode (LED) is on the front of the system unit. The power supply is operating when the LED is lit.

#### Outputs

The power supply provides separate voltage sources for the system board and the drives. The system-board voltages are +5 Vdc, +12 Vdc, and -12 Vdc. The drive voltages are +5 Vdc and +12 Vdc. The following is a list of the approximate power provided for system components.

|                                                            | Maximi  | m Current |

|------------------------------------------------------------|---------|-----------|

| System Component                                           | +12 Vdc | +5 Vdc    |

| Internal Fixed Disk Drives<br>(per power supply connector) | 2.5 A   | 1.5 A     |

| Auxiliary Device                                           | None    | 300 mA    |

| Keyboard                                                   | None    | 275 mA    |

Figure 1-7. Component Maximum Current

The following are the load currents allowed for each Micro Channel connector.

| 1.6 A   |

|---------|

| 0.175 A |

| 0.040 A |

|         |

| Figure 1-8. Channel Load Current

The formulas used to determine the power requirements and the voltage regulation tolerances are in the Micro Channel adapter

design information in the Hardware Interface Technical Reference - Architectures manual.

#### | Output Protection

A short circuit placed on any dc output (between outputs or between an output and dc return) latches all dc outputs into a shutdown state with no damage to the power supply.

| If an overvoltage fault occurs (internal to the power supply), the | power supply latches all dc outputs into a shutdown state before any | output exceeds 130% of its nominal value.

If either of these shutdown states is actuated, the power supply returns to normal operation only after the fault has been removed and the power switch has been turned off for at least ten seconds.

### Voltage Sequencing

At power-on time, the output voltages track within 50 milliseconds of each other when measured at the 50% points.

## | Power Supply Connectors

The power supply provides two 4-pin connectors for internal fixed disk drives. These connectors can be extended to provide power to more than one internal drive as long as the total power does not exceed the specifications shown in Figure 1-7 on page 1-10.

| Pin | Signal    |  |

|-----|-----------|--|

| 1   | + 12 Vdc  |  |

| 2   | DC Return |  |

| 3   | DC Return |  |

| 4   | + 5 Vdc   |  |

| L   |           |  |

Figure 1-9. Voltage Assignments for the Internal Drive Power-Supply Connectors

## **Notes:**

# Section 2. Programmable Option Select

| Description                              |            |    |    |  |  |  |  | . 2-3 |

|------------------------------------------|------------|----|----|--|--|--|--|-------|

| POS Address Map                          |            |    |    |  |  |  |  | . 2-5 |

| Card Selected Feedback                   |            |    |    |  |  |  |  | . 2-6 |

| System Board Setup                       |            |    |    |  |  |  |  |       |

| System Board Enable/Setup Register (Hex  | <b>(</b> 0 | 09 | 4) |  |  |  |  | . 2-7 |

| System Board POS Register 2 (Hex 0102)   |            |    |    |  |  |  |  |       |

| System Board POS Register 3 (Hex 0103)   |            |    |    |  |  |  |  |       |

| Adapter Enable/Setup Register (Hex 0096) |            |    |    |  |  |  |  |       |

## **Notes:**

### **Description**

Programmable Option Select (POS) eliminates the need for switches by replacing their function with programmable registers. This section describes the POS information used specifically by the Model 60 system board. For additional POS information, refer to the Hardware Interface Technical Reference Micro Channel architecture information.

#### Warning:

- IBM recommends that programmable options be set only through the System Configuration utilities. Directly setting the POS registers or CMOS RAM POS parameters can cause multiple assignment of the same system resource, improper operation of the feature, loss of data, or possible damage to the hardware.

- Application programs should not use the adapter identification (ID) unless absolutely necessary. Compatibility problems can result.

- If an adapter and the system board are in setup mode at the same time, bus contention will occur, no useful programming can take place, and damage to the hardware can occur.

- After setup operations are complete, the Adapter Enable/Setup register (hex 0096) should be set to hex 00, and the System Board Enable/Setup register (hex 0094) should be set to hex FF.

- The channel reset bit (bit 7) in the Adapter Enable/Setup register must be 0 to program the adapters.

- The system board does not support 16-bit I/O operations to 8-bit POS registers. Using 16-bit I/O instructions on 8-bit POS registers will cause erroneous data to be written to or read from the registers. Only 8-bit transfers are supported for setup operations.

Setup functions respond to I/O addresses hex 0100 through 0107 only when their unique setup signal is active. The following precautions must be taken before setting individual bits in the POS registers.

#### System Board Video Subsystem Setup:

- Bit 5 in the System Board Enable/Setup register (hex 0094) must be set to 0 to place the system board video into the setup mode.

- Bit 3 in the Adapter Enable/Setup register (hex 0096) must be set to 0 to avoid driving a 'setup' signal to an adapter.

- Bit 7 in the System Board Enable/Setup register (hex 0094) must be set to 1 to avoid driving a 'setup' signal to other system board functions.

#### Adapter Setup:

- Bit 3 in the Adapter Enable/Setup register (hex 0096) must be set to 1 to allow adapter setup.

- Bit 5 in the System Board Enable/Setup register (hex 0094) must be set to 1 to avoid driving a 'setup' signal to the Video Subsystem.

- Bit 7 in the System Board Enable/Setup register (hex 0094) must be set to 1 to avoid driving a 'setup' signal to a system board function.

#### Other System Board Setup:

- Bit 7 in the System Board Enable/Setup register (hex 0094) must be set to 0 to allow setup of other system board functions.

- Bit 3 in the Adapter Enable/Setup register (hex 0096) must be set to 0 to avoid driving a 'setup' signal to an adapter.

- Bit 5 in the System Board Enable/Setup register (hex 0094) must be set to 1 to avoid driving a 'setup' signal to the Video Subsystem.

# **POS Address Map**

The following figure shows the organization of the I/O address space used by POS. The POS registers are 8-bit registers. Bit 0 of POS Register 2 and bits 6 and 7 of POS Register 5 are defined. All other bits in POS Registers 2 through 5 are free-form.

| Address<br>(Hex) | Function                                                                                                                                       |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0094             | System Board Enable/Setup Register                                                                                                             |  |

| 0096             | Adapter Enable/Setup Register                                                                                                                  |  |

| 0100             | POS Register 0 – Adapter Identification Byte (Low Byte)                                                                                        |  |

| 0101             | POS Register 1 - Adapter Identification Byte (High Byte)                                                                                       |  |

| 0102             | POS Register 2 – Option Select Data Byte 1 Bit 0 is Card Enable.                                                                               |  |

| 0103             | POS Register 3 – Option Select Data Byte 2                                                                                                     |  |

| 0104             | POS Register 4 – Option Select Data Byte 3                                                                                                     |  |

| 0105             | POS Register 5 – Option Select Data Byte 4 Bit 7 is the channel check active indicator. Bit 6 is the channel check status-available indicator. |  |

| 0106             | Reserved                                                                                                                                       |  |

| 0107             | Reserved                                                                                                                                       |  |

Figure 2-1. POS I/O Address Map

## **Card Selected Feedback**

When the adapter is addressed, it responds by setting the '-card selected feedback' signal (-CD SFDBK) to active. -CD SFDBK is derived from the address decode and driven by a totem pole driver. It is latched by the system board and can be read through the Card Selected Feedback register at address hex 0091. Diagnostic and automatic configuration programs use this signal to verify the operation of an adapter at a given address or DMA port. This signal must not be active during a setup cycle.

The Card Selected Feedback register is a read-only register at address hex 0091. It allows programs to monitor -CD SFDBK and thereby determine if the video subsystem, system board I/O, or an adapter is addressed and functioning.

| Bit   | Function                |

|-------|-------------------------|

| 7 - 1 | Reserved                |

| 0     | -Card Selected Feedback |

Figure 2-2. Card Selected Feedback Register (Hex 0091)

#### Bits 7 - 1 Reserved.

#### Bit 0

This bit is set to 1 whenever -CD SFDBK was active on a previous cycle or whenever the system board I/O functions (diskette drive, serial, or parallel interfaces) are accessed by an I/O cycle. Reading this register resets the bit to 0.

# System Board Setup

The integrated I/O functions on the system board use POS information during setup. The diskette drive controller, serial port, and parallel port are treated as a single device. The video subsystem is also an integrated part of the system board; however, POS treats it as a separate device. The System Board Enable/Setup register is used to place the system board or video subsystem into the setup mode.

### System Board Enable/Setup Register (Hex 0094)

This is a read/write register; all bits in this register default to 1 (enabled).

| Bit   | Function                             |

|-------|--------------------------------------|

| 7     | Enable/-Setup System Board Functions |

| 6     | Reserved                             |

| 5     | Enable/-Setup Video Subsystem        |

| 4 - 0 | Reserved                             |

Figure 2-3. System Board Enable/Setup Register (Hex 0094)

Bit 7 When this bit is set to 0, various system board I/O functions are placed in the setup mode. The diskette drive controller, serial port, and parallel port are controlled through System Board POS Register 2 (hex 0102). The memory is controlled through System Board POS Register 3 (hex 0103).

When this bit is set to 1, the system board functions are enabled.

#### Bit 6 Reserved.

Bit 5 When this bit is set to 0, the video subsystem is placed in the setup mode and controlled through POS Register 2 (hex 0102). When set to 1, and bit 0 in hex 0102 is set to 1, video is enabled.

Bit 0 of POS Register 2 is the video enable bit. When this bit is set to 0, the video subsystem does not respond to commands, addresses, or data. If video is being generated when the video enable bit is set to 0, the output is still generated. For information on BIOS calls to enable or disable the video, see the IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference.

Note: When the video is disabled, access to the video DAC registers is disabled.

#### Bits 4 - 0 Reserved.

# System Board POS Register 2 (Hex 0102)

When the system board is in the setup mode, the diskette drive controller, serial port, and parallel port are controlled by this read/write register. Reading this register returns the current state of these system board functions.

|   | Bit  | Function                            | · |

|---|------|-------------------------------------|---|

|   | 7    | Disable Parallel Port Extended Mode |   |

|   | 6, 5 | Parallel Port Select                |   |

| 1 | 4    | Enable Parallel Port                |   |

|   | 3    | Serial Port Select                  |   |

| ł | 2    | Enable Serial Port                  |   |

|   | 1    | Enable Diskette Drive Interface     |   |

|   | 0    | Enable System Board                 |   |

Figure 2-4. System Board POS Register 2 (Hex 0102)

- When set to 0, this bit allows the parallel port to be configured as an 8-bit parallel bidirectional interface. When set to 1, this bit disables the bidirectional mode. This bit is set to 0 at power-on, and POST sets it to 1.

- Bits 6, 5 These bits select the configuration of the system board parallel port.

| Bits<br>6 5 | Assignment | Hex Address | Interrupt Level |

|-------------|------------|-------------|-----------------|

| 0 0         | Parallel 1 | 03BC - 03BF | 7               |

| 0 1         | Parallel 2 | 0378 - 037B | 7               |

| 10          | Parallel 3 | 0278 - 027B | 7               |

| 11          | Reserved   |             | ,<br>-          |

Figure 2-5. Parallel Port Select Bits

- When this bit and bit 0 are set to 1, the system board parallel port is enabled.

- When set to 1, this bit sets the system board serial port as Serial 1 (addresses hex 03F8 through 03FF), which uses interrupt level 4. When set to 0, this bit sets the serial port as Serial 2 (addresses hex 02F8 through 02FF), which uses interrupt level 3.

- When this bit and bit 0 are set to 1, the system board serial port is enabled.

- When this bit and bit 0 are set to 1, the diskette drive interface is enabled.

When set to 1, this bit allows bits 4, 2, and 1 to enable and disable their respective devices. When set to 0, this bit disables the diskette drive interface, system board serial port, and system board parallel port, regardless of the state of bits 4, 2, and 1.

#### System Board POS Register 3 (Hex 0103)

With the system board in setup, this register controls the system board memory.

| Bit   | Function                |

|-------|-------------------------|

| 7 - 1 | Reserved                |

| 0     | Enable System Board RAM |

Figure 2-6. System Board POS Register (Hex 0103)

#### Bit 7 - 1 Reserved.

When set to 1, this bit enables the system board memory. When set to 0, this bit disables the memory. All system board memory is enabled or disabled by this operation.

# Adapter Enable/Setup Register (Hex 0096)

The Adapter Enable/Setup register selects the connector to be configured.

| Bit   | Symbol               |  |

|-------|----------------------|--|

| 7     | Channel Reset        |  |

| 6 - 4 | Reserved             |  |

| 3     | Card Setup Enable    |  |

| 2 - 0 | Channel Select 2 - 0 |  |

Figure 2-7. Adapter Enable/Setup Register (Hex 0096)

- When set to 1, this bit activates the 'channel reset' signal to all connectors.

- Bits 6 4 These bits are reserved.

- When set to 1, this bit enables the '-card setup' signal selected by bits 2 through 0.

- Bits 2 0 These bits are the address bits for the '-card setup' signal Connectors 1 through 8 are addressed as 0 through 7, respectively. When bit 3 is set to 1, these bits select the connector that is put into setup.

Each channel connector has a unique '-card setup' signal (-CD SETUP) associated with it. This signal is used to put the adapters in the setup mode, which allows access to the POS registers. The individual connectors are selected through the Adapter Enable/Setup register. Setup information is then read from or written to the selected adapter through I/O addresses hex 0100 through 0107.

#### Notes:

- -CD SETUP only goes active when an operation is performed in the I/O address range hex 0100 through 0107.

- 2. The status of port hex 0096 can be read by software. However, when the port is read, bits 6, 5, and 4 are set to 1.

# Section 3. System Board

| Description                                                                                                                                                                                                                                                                                    |                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Micro Channel Implementation                                                                                                                                                                                                                                                                   | . 3-3                                                                        |

| Exception Reporting                                                                                                                                                                                                                                                                            |                                                                              |

| Adapter Identification                                                                                                                                                                                                                                                                         | . 3-3                                                                        |

| Central Arbiter                                                                                                                                                                                                                                                                                | . 3-3                                                                        |

| Arbitration Bus Priority Assignments                                                                                                                                                                                                                                                           |                                                                              |

| Central Arbiter Programming                                                                                                                                                                                                                                                                    |                                                                              |

| Memory                                                                                                                                                                                                                                                                                         |                                                                              |

| Read-Only Memory Subsystem                                                                                                                                                                                                                                                                     |                                                                              |

| Random Access Memory Subsystem                                                                                                                                                                                                                                                                 | . 3-7                                                                        |

| System Memory Maps                                                                                                                                                                                                                                                                             |                                                                              |

| System Board Memory Connector                                                                                                                                                                                                                                                                  |                                                                              |

| Real-Time Clock/Complementary Metal-Oxide Semiconductor                                                                                                                                                                                                                                        | •                                                                            |

|                                                                                                                                                                                                                                                                                                |                                                                              |

| RAM                                                                                                                                                                                                                                                                                            |                                                                              |

|                                                                                                                                                                                                                                                                                                | 3-10                                                                         |

| RT/CMOS Address Register and NMI Mask (Hex 0070)                                                                                                                                                                                                                                               | 3-10<br>3-11                                                                 |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071)                                                                                                                                                                                                              | 3-10<br>3-11<br>3-11                                                         |

| RT/CMOS Address Register and NMI Mask (Hex 0070)                                                                                                                                                                                                                                               | 3-10<br>3-11<br>3-11<br>3-12                                                 |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D)                                                                                                                                               | 3-10<br>3-11<br>3-11<br>3-12<br>3-13                                         |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D) CMOS RAM Configuration                                                                                                                        | 3-10<br>3-11<br>3-11<br>3-12<br>3-13<br>3-16                                 |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D) CMOS RAM Configuration Miscellaneous System Functions                                                                                         | 3-10<br>3-11<br>3-11<br>3-12<br>3-13<br>3-16<br>3-20                         |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D) CMOS RAM Configuration                                                                                                                        | 3-10<br>3-11<br>3-11<br>3-12<br>3-13<br>3-16<br>3-20<br>3-20                 |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D) CMOS RAM Configuration Miscellaneous System Functions Nonmaskable Interrupt System Control Port B (Hex 0061)                                  | 3-10<br>3-11<br>3-12<br>3-13<br>3-16<br>3-20<br>3-20<br>3-20                 |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D) CMOS RAM Configuration Miscellaneous System Functions Nonmaskable Interrupt System Control Port B (Hex 0061) System Control Port A (Hex 0092) | 3-10<br>3-11<br>3-12<br>3-13<br>3-16<br>3-20<br>3-20<br>3-21                 |

| RT/CMOS Address Register and NMI Mask (Hex 0070) RT/CMOS Data Register (Hex 0071) RT/CMOS RAM I/O Operations Real-Time Clock Bytes (Hex 000-00D) CMOS RAM Configuration Miscellaneous System Functions Nonmaskable Interrupt System Control Port B (Hex 0061)                                  | 3-10<br>3-11<br>3-11<br>3-12<br>3-13<br>3-16<br>3-20<br>3-20<br>3-21<br>3-23 |

### **Notes:**

# **Description**

This section provides information about the Model 60 implementation of the Micro Channel architecture, memory subsystem, and miscellaneous system ports. Additional information on these topics can be found in the Hardware Interface Technical Reference listed in the preface of this manual.

# Micro Channel Implementation

The POST routines and registers used to implement programmable features of the Micro Channel architecture may vary from system to system. This section provides information about the Model 60 implementation of the Micro Channel architecture.

### | Exception Reporting

| Exceptions should be reported using the asynchronous channel check | procedure. The synchronous channel check procedure is not | supported.

### Adapter Identification

When the system is powered on, an adapter can issue an ID of hex 0000 for up to 1 second after channel reset to indicate it is not ready. Any adapter that continues to issue an adapter ID of hex 0000 (not ready) for more than 1 second is considered defective. On the Model 60, if the channel reset was caused by a keyboard sequence or a program routine, this time is reduced to 740 milliseconds.

#### **Central Arbiter**

The central arbitration control point gives intelligent subsystems on the channel the ability to share and control the system. It allows burst data transfers and prioritization of control between devices. This arbiter supports up to 16 arbitrating devices.

## **Description**

This section provides information about the Model 60 implementation of the Micro Channel architecture, memory subsystem, and miscellaneous system ports. Additional information on these topics can be found in the Hardware Interface Technical Reference listed in the preface of this manual.

## Micro Channel Implementation

The POST routines and registers used to implement programmable features of the Micro Channel architecture may vary from system to system. This section provides information about the Model 60 implementation of the Micro Channel architecture.

### | Exception Reporting

| Exceptions should be reported using the asynchronous channel check procedure. The synchronous channel check procedure is not | supported.

### Adapter Identification

When the system is powered on, an adapter can issue an ID of hex 0000 for up to 1 second after channel reset to indicate it is not ready. Any adapter that continues to issue an adapter ID of hex 0000 (not ready) for more than 1 second is considered defective. On the Model 60, if the channel reset was caused by a keyboard sequence or a program routine, this time is reduced to 740 milliseconds.

#### **Central Arbiter**

The central arbitration control point gives intelligent subsystems on the channel the ability to share and control the system. It allows burst data transfers and prioritization of control between devices. This arbiter supports up to 16 arbitrating devices.

#### **Central Arbiter Programming**

The central arbitration control point provides access to programmable options through the Arbitration register, which is accessed at I/O address hex 0090. The bits are defined differently for read and write operations, as shown in the following figures.

| Bit   | Definition                         |

|-------|------------------------------------|

| 7     | Enable System Microprocessor Cycle |

| 6     | Arbitration Mask                   |

| 5     | Enable Extended Arbitration        |

| 4 - 0 | Reserved                           |

Figure 3-2. Arbitration Register, Write to Hex 0090

| Bit   | Definition                                           |

|-------|------------------------------------------------------|

| 7     | Enable System Microprocessor Cycle                   |

| 6     | Arbitration Masked by NMI                            |

| 5     | Bus Time-out                                         |

| 4     | Reserved                                             |

| 3 - 0 | Value of Arbitration Bus During Previous Grant State |

Figure 3-3. Arbitration Register, Read Hex 0090

Bit 7 Setting this bit to 1 enables system microprocessor cycles during arbitration cycles. This bit can be set to 0 if an arbitrating device requires total control of the channel bandwidth. This bit is set to 0 by a system reset.

Reading this bit as a 1 indicates system microprocessor cycles are enabled during arbitration.

Bit 6 Setting this bit to 1 causes the central arbitration control point to enter the arbitration state. The system microprocessor controls the channel until this bit is reset to 0. This bit is set to 0 by a system reset.

Reading this bit as a 1 indicates that an NMI has occurred and has masked arbitration.

**Warning:** This bit should be set to 1 only by diagnostic routines and system error-recovery routines.

Bit 5 Setting this bit to 1 enables extended arbitration. The minimum arbitration cycle is 300 nanoseconds; this bit extends that minimum cycle to 600 nanoseconds. This bit is set to 0 during a system reset.

Reading this bit as a 1 indicates that a bus time-out has occurred, and resets bit 6 in this register to 0.

- Bit 4 This bit is reserved and should be 0.

- Bits 3 0 These bits are undefined for a write operation and should be set to 0.

Reading these bits returns the arbitration level of the arbiter controlling the channel during the most recent grant state. This information allows the system microprocessor to determine the arbitration level of the device that caused a bus time-out.

# **Memory**

The Model 60 system uses the following types of memory:

- Read-only memory (ROM)

- Random access memory (RAM)

- Real-time Clock and CMOS RAM.

### **Read-Only Memory Subsystem**

The ROM subsystem system board consists of four 32Kb by 8-bit modules in a 64Kb by 16-bit arrangement (Kb equals 1024 bits).

ROM is not parity-checked and is assigned addresses at the top of the first and last 1MB of address space (hex 0E0000 and FE0000).

### **Random Access Memory Subsystem**

The RAM subsystem on the system board starts at address hex 000000 of the 16MB address space. It consists of 1MB of RAM modules.

The system board uses four memory module packages that operate with one wait state. Memory-refresh typically occurs once every 15 microseconds.

The timing of the memory signals on the system board is similar to the Hitachi" HB61009BR-15, 150-nanosecond DRAM or equivalent.

<sup>&</sup>quot; Hitachi is a trademark of the Hitachi Corporation.

# **System Memory Maps**

The following figure shows the mapping of the memory locations on the Model 60. A 256-byte portion of this RAM is reserved as a BIOS data area. A 1KB portion of this RAM is reserved as an extended BIOS data area. See the IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference for details.

| System Board RAM * Video RAM I/O Expansion ROM             |

|------------------------------------------------------------|

| Video RAM                                                  |

|                                                            |

|                                                            |

| System Board ROM                                           |

| System Board RAM                                           |

| el Expansion Memory Addresses                              |

| System Board ROM                                           |

| System Board ROM etup mode, the system board memory can be |

|                                                            |

Figure 3-4. System Memory Map

### **System Board Memory Connector**

The system board has four 30-pin connectors and comes with four 256KB memory module packages installed. The following figure shows the pin assignments and signal definitions for these connectors.

| Pin | 1/0 | Signal                      | Pin | 1/0 | Signal                      |

|-----|-----|-----------------------------|-----|-----|-----------------------------|

| 1   | N/A | + 5 Vdc ✓                   | 2   | ī   | -Column Address             |

|     |     |                             |     |     | Strobe ~                    |

| 3   | 1/0 | Data Bit 1 DØ               | 4   | l   | Address Bit 1 🖊 🤣           |

| 5   | 1   | Address Bit 2 A1            | 6   | I/O | Data Bit 2 <sup>D∕4</sup>   |

| 7   | ı   | Address Bit 3 Az            | 8   | 1   | Address Bit 4 A3            |

| 9   | N/A | Ground                      | 10  | 1/0 | Data Bit 3 ▷ ≥              |

| 11  | 1   | Address Bit 5 A4            | 12  | 1   | Address Bit 6 AC            |

| 13  | 1/0 | Data Bit 4 P3               | 14  | 1   | Address Bit 7 A6            |

| 15  | 1   | Address Bit 8 A∃            | 16  | 1/0 | Data Bit 5 DY               |

| 17  | 1   | Address Bit 9 Ag            | 18  | N/A | No Connection A9            |

| 19  | 1   | Reserved A40                | 20  | 1/0 | Data Bit 6 ⊅ ⊊              |

| 21  | 1   | -Write Strobe ₩E            | 22  | N/A | Ground 🗸                    |

| 23  | 1/0 | Data Bit 7 D6               | 24  | 0   | Presence Detect NC          |

| 25  | 1/0 | Data Bit 8 ▷∋               | 26  | 0   | Presence Detect DAT Git QUI |

| 27  | 1   | Reserved RAS                | 28  | N/A | No Connection -(ASP         |

| 29  | 1/0 | Data Bit 9 (Parity) DPAR IN | 30  | N/A | +5 Vdc ✓                    |

Figure 3-5. System Board Memory Connector

# Real-Time Clock/Complementary Metal-Oxide Semiconductor RAM

The real-time clock/complementary metal-oxide semiconductor RAM (RT/CMOS) chip contains the real-time clock and 64 bytes of CMOS RAM. The internal clock circuitry uses 14 bytes of this memory, and the rest is allocated to configuration and system status information.

In addition to the 64 bytes of CMOS RAM, a 2KB CMOS RAM extension is provided for configuration and other system information.

A 6-Vdc lithium battery maintains voltage to the RT/CMOS RAM and 2KB CMOS RAM extension when the power supply is not in operation.

The system cover can be locked to prevent battery removal and loss of password and configuration information.

The following figure shows the RT/CMOS RAM bytes and their addresses.

| Address (Hex) | RT/CMOS RAM Bytes                   |

|---------------|-------------------------------------|

| 000 - 00D     | Real-Time Clock Bytes               |

| 00E           | Diagnostic Status Byte              |

| 00F           | Shutdown Status Byte                |

| 010           | Diskette Drive Type Byte            |

| 011           | First Fixed Disk Drive Type Byte    |

| 012           | Second Fixed Disk Drive Type Byte   |

| 013           | Reserved                            |

| 014           | Equipment Byte                      |

| 015 - 016     | Low and High Base Memory Bytes      |

| 017 - 018     | Low and High Expansion Memory Bytes |

| 019 - 031     | Reserved                            |

| 032 - 033     | Configuration CRC Bytes             |

| 034           | Reserved                            |

| 035 - 036     | Low and High Useable Memory Bytes   |

| 037           | Date Century Byte                   |

| 038 - 03F     | Reserved                            |

Figure 3-6. RT/CMOS RAM Address Map

### RT/CMOS Address Register and NMI Mask (Hex 0070)

This register is used in conjunction with the port at hex 0071 to read and write the RT/CMOS RAM bytes.

| Bit   | Function            |

|-------|---------------------|

| 7     | NMI Mask            |

| 6     | Reserved            |

| 5 - 0 | RT/CMOS RAM Address |

Figure 3-7. RT/CMOS Address Register and NMI Mask (Hex 0070)

**Warning:** The operation following a write to hex 0070 should access port hex 0071; otherwise intermittent malfunctions and unreliable operation of the RT/CMOS RAM can occur.

- When this bit is set to 1, the NMI is masked off (the NMI is disabled). This bit is set to 1 by a power-on reset and is a write-only bit.

- Bit 6 Reserved.

- Bits 5 0 These bits are used to select RT/CMOS RAM addresses.

#### RT/CMOS Data Register (Hex 0071)

This port is used in conjunction with the address register at hex 0070 to read and write the RT/CMOS RAM bytes.

| Bit   | Function     | $\neg$ |

|-------|--------------|--------|

| 7 - 0 | RT/CMOS Data |        |

Figure 3-8. RT/CMOS Data Register (Hex 0071)

# **RT/CMOS RAM I/O Operations**

During I/O operations to the RT/CMOS RAM addresses, interrupts should be masked to prevent other interrupt service routines from changing the CMOS address register before data is read or written. After I/O operations, the RT/CMOS and NMI Mask register (hex 0070) should be left pointing to Status Register D (hex 00D).

**Warning:** The operation following a write to hex 0070 should access hex 0071; otherwise intermittent malfunctions and unreliable operation of the RT/CMOS RAM can occur.

The following steps are required to perform I/O operations to the RT/CMOS RAM addresses:

- 1. Write the RT/CMOS RAM address to the RT/CMOS and NMI Mask register (hex 0070).

- 2. Write the data to address hex 0071.

Reading RT/CMOS RAM requires the following steps:

- Write the RT/CMOS RAM address to the RT/CMOS and NMI Mask register (hex 0070).

- 2. Read the data from address hex 0071.

#### Real-Time Clock Bytes (Hex 000-00D)

Bit definitions and addresses for the real-time clock bytes are shown in the following figure.

| Address (Hex) | Function          | Byte Number |  |

|---------------|-------------------|-------------|--|

| 000           | Seconds           | 0           |  |

| 001           | Second Alarm      | 1           |  |

| 002           | Minutes           | 2           |  |

| 003           | Minute Alarm      | 3           |  |

| 004           | Hours             | 4           |  |

| 005           | Hour Alarm        | 5           |  |

| 006           | Day of Week       | 6           |  |

| 007           | Date of Month     | 7           |  |

| 800           | Month             | 8           |  |

| 009           | Year              | 9           |  |

| 00A           | Status Register A | 10          |  |

| 00B           | Status Register B | 11          |  |

| 00C           | Status Register C | 12          |  |

| Q00           | Status Register D | 13          |  |

Figure 3-9. Real-Time Clock Bytes

Note: The Setup program initializes status registers A, B, C, and D when the time and date are set. Interrupt hex 1A is the BIOS interface to read and set the time and date and it initializes the register the same way as the Setup program.

#### Status Register A (Hex 00A)

| Bit   | Function            |

|-------|---------------------|

| 7     | Update in Progress  |

| 6 - 4 | 22-Stage Divider    |

| 3 - 0 | Rate Selection Bits |

Figure 3-10. Status Register A

- When set to 1, this bit indicates the time-update cycle is in progress. When set to 0, it indicates the current date and time can be read.

- Bits 6 4 These three divider-selection bits identify which time-base frequency is being used. The system initializes these bits to binary 010, which selects a 32.768 kHz time-base. This is the only value supported by the system for proper time-keeping.

Bits 3 - 0 These bits allow the selection of a divider output frequency. The system initializes the rate selection bits to a binary 0110, which selects a 1.024 kHz square-wave output frequency and a 976.562-microsecond periodic interrupt rate.

### Status Register B (Hex 00B)

| Ві | it | Function                       |  |

|----|----|--------------------------------|--|

| 7  | ,  | Set                            |  |

| 6  | i  | Periodic Interrupt Enable      |  |

| 5  | ;  | Alarm Interrupt Enable         |  |

| 4  | ļ  | Update-Ended Interrupt Enabled |  |

| 3  | 1  | Square Wave Enabled            |  |

| 2  | !  | Date Mode                      |  |

| 1  |    | 24-Hour Mode                   |  |

| 0  | 1  | Daylight Savings Enabled       |  |

Figure 3-11. Status Register B

- When set to 0, this bit updates the cycle, normally by advancing the counts at a rate of one per second. When set to 1, this bit immediately ends any update cycle in progress, and the program can initialize the 14 time bytes without any further updates occurring until this bit is set to 0.

- This bit is a read/write bit that allows an interrupt to occur at a rate specified by the rate and divider bits in Status Register A. When set to 1, this bit enables the interrupt. The system initializes this bit to 0.

- When set to 1, this bit enables the alarm interrupt. The system initializes this bit to 0.

- When set to 1, this bit enables the update-ended interrupt.

The system initializes this bit to 0.

- When set to 1, this bit enables the square-wave frequency as set by the rate-selection bits in Status Register A. The system initializes this bit to 0.

- Bit 2 This bit indicates if the time-and-date calendar updates use binary or binary-coded-decimal (BCD) formats. When set to 1, this bit indicates a binary format. The system initializes this bit to 0.

- This bit establishes if the hours byte is in the 24-hour or 12-hour mode. When set to 1, this bit indicates the 24-hour mode. The system initializes this bit to 1.

When set to 1, this bit enables the daylight savings time mode. When set to 0, it disables the mode, and the clock reverts to standard time. The system initializes this bit to 0.

#### Status Register C (Hex 00C)

| Bit | Function                    |

|-----|-----------------------------|

| 7   | Interrupt Request Flag      |

| 6   | Periodic Interrupt Flag     |

| 5   | Alarm Interrupt Flag        |

| 4   | Update-Ended Interrupt Flag |

| 3-0 | Reserved                    |

Figure 3-12. Status Register C

Note: Interrupts are enabled by bits 6, 5, and 4 in Status Register B.

This bit is used in conjunction with bits 6, 5, and 4. When set to 1, this bit indicates that an interrupt has occurred; bits 6, 5, and 4 indicate the type of interrupt.

Bit 6 When set to 1, this bit indicates that a periodic interrupt occurred.

Bit 5 When set to 1, this bit indicates that an alarm interrupt occurred.

When set to 1, this bit indicates that an update-ended interrupt occurred.

Bits 3 - 0 Reserved.

### Status Register D (Hex 00D)

| Bit | Function  |  |

|-----|-----------|--|

| 7   | Valid RAM |  |

| 6-0 | Reserved  |  |

Figure 3-13. Status Register D

Bit 7 This read-only bit monitors the power-sense pin. A low state of this pin indicates a loss of power to the real-time clock (dead battery). When set to 1, this bit indicates that the real-time clock has power. When set to 0, it indicates that the real-time clock has lost power.

#### Bits 6 - 0 Reserved.

# **CMOS RAM Configuration**

The following shows the bit definitions for the CMOS RAM configuration bytes.

# Diagnostic Status Byte (Hex 00E)

| Bit | Function                                            |

|-----|-----------------------------------------------------|

| 7   | Real-Time Clock Chip Power                          |

| 6   | Configuration Record and Checksum Status            |

| 5   | Incorrect Configuration                             |

| 4   | Memory Size Miscompare                              |

| 3   | Fixed Disk Controller/Drive C Initialization Status |

| 2   | Time Status Indicator                               |

| 1   | Adapter Configuration Miscompare                    |

| 0   | Adapter ID Time-Out                                 |

| Figure | 3-14. Diagnostic Status Byte                                                                                                                                                                                                                    |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7  | When set to 1, this bit indicates the real-time clock chip lost power.                                                                                                                                                                          |

| Bit 6  | When this bit is set to 1, the checksum is incorrect.                                                                                                                                                                                           |

| Bit 5  | This is a check, at power-on time, of the Equipment byte. When set to 1, the configuration information is incorrect. Power-on checks require that at least one diskette drive be installed (bit 0 of the Equipment byte, hex 014, is set to 1). |

| Bit 4  | When set to 1, this bit indicates the power-on check determined that the memory size is not the same as in the configuration record.                                                                                                            |

| Bit 3  | When set to 1, this bit indicates that the controller or drive C failed initialization, which prevents the system from attempting a power-on reset.                                                                                             |

| Bit 2  | When set to 0, this bit indicates the time is valid. When set to 1, this bit indicates the time is invalid.                                                                                                                                     |

| Bit 1  | This bit indicates if the installed adapters match the configuration information. When this bit is set to 1, the adapters do not match the configuration information.                                                                           |

| Bit 0  | When set to 1, this bit indicates a time-out occurred while an adapter ID was being read.                                                                                                                                                       |

**Shutdown Status Byte (Hex 00F):** This byte is defined by the power-on diagnostic programs.

Diskette Drive Type Byte (Hex 010): This byte indicates the type of diskette drive installed.

| Bit   | Function                   |  |

|-------|----------------------------|--|

| 7 - 4 | First Diskette Drive Type  |  |

| 3-0   | Second Diskette Drive Type |  |

Figure 3-15. Diskette Drive Type Byte

Bits 7 - 4 These bits indicate the first diskette drive type, as shown in the following figure.

| Bits<br>7 6 5 4      | Function                                                |

|----------------------|---------------------------------------------------------|

| 0000                 | No drive present                                        |

| 0001                 | Double-sided diskette drive (48 tracks per inch, 360KB) |

| 0011                 | High-capacity diskette drive (720KB)                    |

| 0100                 | High-density diskette drive (1.44MB)                    |

| All combinations tha | at are not shown are reserved.                          |

Figure 3-16. Diskette Drive Type Byte (Bits 7 - 4)